# INFRARED REMOTE CONTROL TRANSMITTER (RC-5)

## **GENERAL DESCRIPTION**

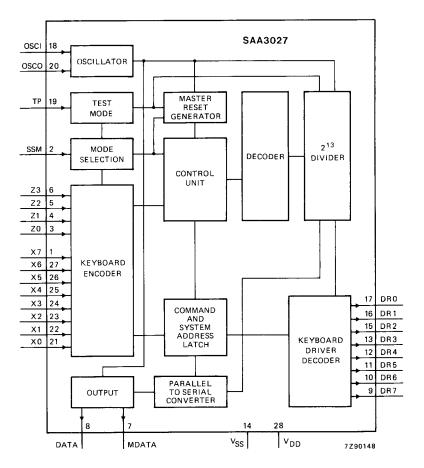

The SAA3027 is intended for a general purpose (RC-5) infrared remote control system. The device can generate 2048 different commands and utilizes a keyboard with a single-pole switch per key. The commands are arranged so that 32 systems can be addressed, each system containing 64 different commands.

The circuit response to legal (one key pressed at a time) and illegal (more than one key pressed at a time) keyboard operation is specified later in this publication (see KEY ACTIVITIES).

## **Features**

- Transmitter for 32 x 64 commands

- One transmitter controls 32 systems

- Very low current consumption

- For infrared transmission link

- Transmission by biphase technique

- Short transmission times; speed-up of system reaction time

- · LC oscillator; no crystal required

- Input protection

- Test mode facility

## QUICK REFERENCE DATA

| Supply voltage range                | V <sub>DD</sub>  | 4,75 to 12,6                | V       |

|-------------------------------------|------------------|-----------------------------|---------|

| Input voltage range                 | $v_l$            | -0,5 to (V <sub>DD</sub> +0 | 0,5) V* |

| Input current                       | ± I <sub>I</sub> | max. 10                     | mΑ      |

| Output voltage range                | $v_0$            | –0,5 to (V <sub>DD</sub> +0 | 0,5) V* |

| Output current                      | ± IO             | max.10                      | mΑ      |

| Operating ambient temperature range | T <sub>amb</sub> | -25 to +85                  | oC      |

<sup>\*</sup> V<sub>DD</sub> + 0,5 V not to exceed 15 V.

## **PACKAGE OUTLINE**

28-lead DIL; plastic (SOT117).

Fig. 1 Block diagram.

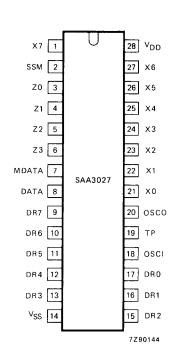

Fig. 2 Pinning diagram.

| PINNI                                  | NG                                           |                                                              |

|----------------------------------------|----------------------------------------------|--------------------------------------------------------------|

| 14<br>28                               | ${\sf v}_{\sf SS} \ {\sf v}_{\sf DD}$        | negative supply (ground)<br>positive supply                  |

| 21<br>22<br>23<br>24<br>25<br>26<br>27 | X0<br>X1<br>X2<br>X3<br>X4<br>X5<br>X6<br>X7 | keyboard command inputs with P-channel pull-up transistors   |

| 3<br>4<br>5<br>6                       | Z0<br>Z1<br>Z2<br>Z3                         | keyboard system inputs with P-channel pull-up transistors    |

| 2<br>19                                | SSM<br>TP                                    | system mode selection input test pin                         |

| 18<br>20                               | OSC1<br>OSC0                                 | oscillator input<br>oscillator output                        |

| 17<br>16<br>15<br>13<br>12<br>11<br>10 | DRO DR1 DR2 DR3 DR4 DR5 DR6 DR7              | scan driver outputs with open<br>drain N-channel transistors |

| 7<br>8                                 | MDATA<br>DATA                                | remote signal outputs (3-state outputs)                      |

|                                        |                                              |                                                              |

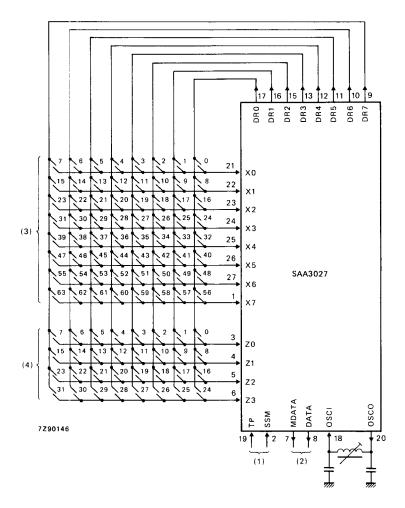

- (1) Programming inputs for operating modes, test mode and reset.

- (2) Remote signal outputs.

- (3) Keyboard command code matrix 8 x 8.

- (4) Keyboard system code matrix 4 x 8.

Fig. 3 Keyboard interconnection.

#### **FUNCTIONAL DECRIPTION**

## Combined system mode (SSM = L.OW)

The X and Z-lines are active HIGH in the quiescent state. Legal key operation either in the X-DR or Z-DR matrix starts the debounce cycle. When the contact is made for two bit times without interruption, the oscillator-enable signal is latched and the key may be released. Interruption within the two bit times resets the internal action. At the end of the debounce time, the DR-outputs are switched off and two scan cycles are started, switching on the DR-outputs one by one. When a Z or X-input senses a LOW level, a latch-enable signal is fed to the system address or command latches, depending on whether sensing was found in the Z or X-input matrix. After latching a system address number, the device will generate the last command (i.e. all command bits '1') in the chosen system as long as the key is pressed. Latching of a command number causes the device to generate this command together with the system address number stored in the system address latch. Releasing the key will reset the internal action if no data is transmitted at that time. Once the transmission is started, the signal will be finished completely.

## Single system mode (SSM = HIGH)

The X-lines are active HIGH in the quiescent state; the pull-up transistors of the Z-lines are switched off and the inputs are disabled. Only legal key operation in the X-DR matrix starts the debounce cycle. When the contact is made for two bit times without interruption, the oscillator-enable signal is latched and the key may be released. Interruption within the two bit times resets the internal action. At the end of the debounce time, the pull-up transistors in the X-lines are switched off, those in the Z-lines are switched on during the first scan cycle. The wired connection in the Z-matrix is then translated into a system address number and stored in the system address latch. At the end of the first scan cycle the pull-up transistors in the Z-lines are switched off and the inputs are disabled again, while the transistors in the X-lines are switched on. The second scan cycle produces the command number which, after latching, is transmitted together with the system address number.

## Inputs

The command inputs X0 to X7 carry a logical '1' in the quiescent state by means of an internal pull-up transistor. When SSM is LOW, the system inputs Z0 to Z3 also carry a logical '1' in the quiescent state by means of an internal pull-up transistor.

When SSM is HIGH, the transistors are switched off and no current flows via the wired connection in the Z-DR matrix.

#### Oscillator

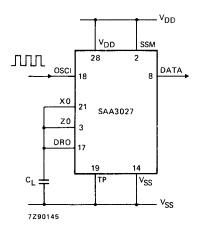

OSCI and OSCO are the input/output respectively of a two-pin oscillator. The oscillator is formed externally by one inductor and two capacitors and operates at 72 kHz (typical).

#### Key-release detection

An extra control bit is added which will be complemented after key-release. In this way the decoder gets an indication that shows if the next code is to be considered as a new command. This is very important for multi-digit entry (e.g. by channel numbers or Teletext/Viewdata pages). The control bit will only be complemented after finishing at least one code transmission. The scan cycles are repeated before every code transmission, so that, even by 'take-over' of key operation during code transmission, the correct system and command numbers are generated.

## FUNCTIONAL DESCRIPTION (continued)

## Outputs

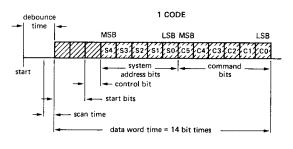

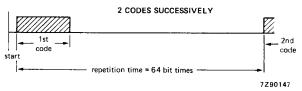

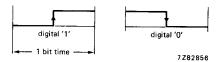

The output DATA carries the generated information according to the format given in Fig. 4 and Tables 1 and 2. The code is transmitted in biphase; definitions of logical '1' and '0' are given in Fig. 5.

The code consists of four parts:

- Start part formed by 2 bits (two times a logical '1');

- Control part formed by 1 bit;

- System part formed by 5 bits;

- Command part formed by 6 bits.

The output MDATA carries the same information as output DATA but is modulated on a carrier frequency of half the oscillator frequency, so that each bit is presented as a burst of 32 oscillator periods. To reduce power consumption, the carrier frequency has a 25% duty cycle.

In the quiescent state, both outputs are non-conducting (3-state outputs). The scan drivers DR0 to DR7 are of the open drain N-channel type and are conducting in the quiescent state of the circuit. After a legal key operation, a scanning procedure is started so that they are switched into the conducting state one after the other.

## Reset action

The circuit will be reset immediately when a key release occurs during:

- debounce time:

- between two codes.

When a key release occurs during scanning of the matrix, a reset action will be accomplished if:

- the key is released while one of the driver outputs is in the low-ohmic '0' state;

- the key is released before detection of that key;

- there is no wired connection in the Z-DR matrix while SSM is HIGH.

#### Test pin

The test pin TP is an input which can be used for testing purposes.

When LOW, the circuit operates normally.

When HIGH, all pull-up transistors are switched off, the control bit is set to zero and the output data is  $2^6$  times faster than normal.

When Z2 = Z3 = LOW, the counter will be reset to zero.

#### **KEY ACTIVITIES**

Every connection of one X-input and one DR-output is recognized as a legal keyboard operation and causes the device to generate the corresponding code.

Activating more than one X-input at a time is an illegal keyboard operation and no circuit action is taken (oscillator does not start).

When SSM is LOW, every connection of one Z-input and one DR-output is recognized as a legal keyboard operation and causes the device to generate the corresponding code.

Activating two or more Z-inputs, or Z-inputs and X-inputs, at one time is an illegal keyboard operation and no circuit action is taken.

When SSM is HIGH, a wired connection must be made between a Z-input and a DR-output. If no connection is made, the code is not generated.

When one X or Z-input is connected to more than one DR-output, the last scan signal is considered legal.

The maximum allowable value of the contact series resistance of the keyboard switches is 10 k $\Omega$ .

Z2 or Z3 must be connected to VDD to avoid unwanted supply current.

Fig. 4 DATA output format (RC-5).

Fig. 5 Biphase transmission code; 1 bit time =  $2^7 \times T_{\mbox{OSC}}$  = 1,778 ms (typical), where  $T_{\mbox{OSC}}$  is the oscillator period time.

Table 1 Command matrix X-DR

| code<br>no. | X-lines<br>X |   |   |   |   |   |   |   |   |   | [ | DR-lines<br>DR |   |   |   |   |   |   |   | command bits<br>C |   |   |  |  |  |  |  |

|-------------|--------------|---|---|---|---|---|---|---|---|---|---|----------------|---|---|---|---|---|---|---|-------------------|---|---|--|--|--|--|--|

| 110.        | 0            | 1 | 2 |   | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3              | 4 | 5 | 6 | 7 | 5 | 4 | 3 | 2                 | 1 | 0 |  |  |  |  |  |

| 0           | •            |   |   |   |   |   |   |   | • |   | - |                |   |   |   |   | 0 | 0 | 0 | 0                 | 0 | 0 |  |  |  |  |  |

| 1           | •            |   |   |   |   |   |   |   |   | • |   |                |   |   |   |   | 0 | 0 | 0 | 0                 | 0 | 1 |  |  |  |  |  |

| 2           | •            |   |   |   |   |   |   |   |   |   | • |                |   |   |   |   | 0 | 0 | 0 | 0                 | 1 | 0 |  |  |  |  |  |

| 3           | •            |   |   |   |   |   |   |   |   |   |   | •              |   |   |   |   | 0 | 0 | 0 | 0                 | 1 | 1 |  |  |  |  |  |

| 4           | •            |   |   |   |   |   |   |   |   |   |   |                | • |   |   |   | 0 | 0 | 0 | 1                 | 0 | 0 |  |  |  |  |  |

| 5           | •            |   |   |   |   |   |   |   |   |   |   |                |   | • |   |   | 0 | 0 | 0 | 1                 | 0 | 1 |  |  |  |  |  |

| 6           | •            |   |   |   |   |   |   |   |   |   |   |                |   |   | • |   | 0 | 0 | 0 | 1                 | 1 | 0 |  |  |  |  |  |

| 7           | •            |   |   |   |   |   |   |   |   |   |   |                |   |   |   | • | 0 | 0 | 0 | 1                 | 1 | 1 |  |  |  |  |  |

| 8           |              | • |   |   |   |   |   |   | • |   |   |                |   |   |   |   | 0 | 0 | 1 | 0                 | 0 | 0 |  |  |  |  |  |

| 9           |              | • |   |   |   |   |   |   |   | • |   |                |   |   |   |   | 0 | 0 | 1 | 0                 | 0 | 1 |  |  |  |  |  |

| 10          |              | • |   |   |   |   |   |   |   |   | • |                |   |   |   |   | 0 | 0 | 1 | 0                 | 1 | 0 |  |  |  |  |  |

| 11          |              | • |   |   |   |   |   |   |   |   |   | •              |   |   |   |   | 0 | 0 | 1 | 0                 | 1 | 1 |  |  |  |  |  |

| 12          |              | • |   |   |   |   |   |   |   |   |   |                | • |   |   |   | 0 | 0 | 1 | 1                 | 0 | 0 |  |  |  |  |  |

| 13          |              | • |   |   |   |   |   |   |   |   |   |                |   | • |   |   | 0 | 0 | 1 | 1                 | 0 | 1 |  |  |  |  |  |

| 14          |              | • |   |   |   |   |   |   |   |   |   |                |   |   | • |   | 0 | 0 | 1 | 1                 | 1 | 0 |  |  |  |  |  |

| 15          |              | • |   |   |   |   |   |   |   |   |   |                |   |   |   | • | 0 | 0 | 1 | 1                 | 1 | 1 |  |  |  |  |  |

| 16          |              |   | • |   |   |   |   |   | • |   |   |                |   |   |   |   | 0 | 1 | 0 | 0                 | 0 | 0 |  |  |  |  |  |

| 17          |              |   | • |   |   |   |   |   |   | • |   |                |   |   |   |   | 0 | 1 | 0 | 0                 | 0 | 1 |  |  |  |  |  |

| 18          | İ            |   | • |   |   |   |   |   |   |   | • |                |   |   |   |   | 0 | 1 | 0 | 0                 | 1 | 0 |  |  |  |  |  |

| 19          |              |   | • |   |   |   |   |   |   |   |   | •              |   |   |   |   | 0 | 1 | 0 | 0                 | 1 | 1 |  |  |  |  |  |

| 20          |              |   | • |   |   |   |   |   |   |   |   |                | • |   |   | ĺ | 0 | 1 | 0 | 1                 | 0 | 0 |  |  |  |  |  |

| 21          |              |   | • |   |   |   |   |   |   |   |   |                |   | • |   |   | 0 | 1 | 0 | 1                 | 0 | 1 |  |  |  |  |  |

| 22          |              |   | • |   |   |   |   |   |   |   |   |                |   |   | • |   | 0 | 1 | 0 | 1                 | 1 | 0 |  |  |  |  |  |

| 23          |              |   | • |   |   |   |   |   |   |   |   |                |   |   |   | • | 0 | 1 | 0 | 1                 | 1 | 1 |  |  |  |  |  |

| 24          |              |   |   | • |   |   |   |   | • |   |   |                |   |   |   |   | 0 | 1 | 1 | 0                 | 0 | 0 |  |  |  |  |  |

| 25          |              |   |   | • |   |   |   |   |   | • |   |                |   |   |   |   | 0 | 1 | 1 | 0                 | 0 | 1 |  |  |  |  |  |

| 26          |              |   |   | • |   |   |   |   |   |   | • |                |   |   |   | ļ | 0 | 1 | 1 | 0                 | 1 | 0 |  |  |  |  |  |

| 27          |              |   |   | • |   |   |   |   |   |   |   | •              |   |   |   |   | 0 | 1 | 1 | 0                 | 1 | 1 |  |  |  |  |  |

| 28          |              |   |   | • |   |   |   |   |   |   |   |                | • |   |   |   | 0 | 1 | 1 | 1                 | 0 | 0 |  |  |  |  |  |

| 29          |              |   |   | • |   |   |   |   |   |   |   |                |   | • |   |   | 0 | 1 | 1 | 1                 | 0 | 1 |  |  |  |  |  |

| 30          |              |   |   | • |   |   |   |   |   |   |   |                |   |   | • |   | 0 | 1 | 1 | 1                 | 1 | 0 |  |  |  |  |  |

| 31          |              |   |   | • |   |   |   |   |   |   |   |                |   |   |   | • | 0 | 1 | 1 | 1                 | 1 | 1 |  |  |  |  |  |

| code     | X-lines |   |   |   |   |   |   |          |   | DR-lines |   |   |   |   |   |   |   |   | command bits |   |   |   |  |  |  |

|----------|---------|---|---|---|---|---|---|----------|---|----------|---|---|---|---|---|---|---|---|--------------|---|---|---|--|--|--|

| no.      | X       |   |   |   |   |   |   |          |   | DR       |   |   |   |   |   |   | C |   |              |   |   |   |  |  |  |

| 110.     | 0       | 1 | 2 | 3 | 4 | 5 | 6 | 7        | 0 | 1        | 2 | 3 | 4 | 5 | 6 | 7 | 5 | 4 | 3            |   | 1 | 0 |  |  |  |

|          | -       |   |   |   |   |   |   | <u> </u> | - |          |   |   |   |   |   |   |   |   |              |   |   |   |  |  |  |

| 32       |         |   |   |   | • |   |   |          | • |          |   |   |   |   |   |   | 1 | 0 | 0            | 0 | 0 | 0 |  |  |  |

| 33       |         |   |   |   | • |   |   |          |   | •        |   |   |   |   |   |   | 1 | 0 | 0            | 0 | 0 | 1 |  |  |  |

| 34       |         |   |   |   | • |   |   |          |   |          | • |   |   |   |   |   | 1 | 0 | 0            | 0 | 1 | 0 |  |  |  |

| 35       |         |   |   |   | • |   |   |          |   |          |   | • |   |   |   |   | 1 | 0 | 0            | 0 | 1 | 1 |  |  |  |

| 36       |         |   |   |   | • |   |   |          |   |          |   |   | • |   |   |   | 1 | 0 | 0            | 1 | 0 | 0 |  |  |  |

| 37       |         |   |   |   | • |   |   |          | ļ |          |   |   |   | • |   |   | 1 | 0 | 0            | 1 | 0 | 1 |  |  |  |

| 38       |         |   |   |   | • |   |   |          |   |          |   |   |   |   | • |   | 1 | 0 | 0            | 1 | 1 | 0 |  |  |  |

| 39       |         |   |   |   | • |   |   |          |   |          |   |   |   |   |   | • | 1 | 0 | 0            | 1 | 1 | 1 |  |  |  |

| 40       |         |   |   |   |   | • |   |          |   |          |   |   |   |   |   |   | 1 | 0 | 1            | 0 | 0 | 0 |  |  |  |

| 41       |         |   |   |   |   | • |   |          |   | •        |   |   |   |   |   |   | 1 | 0 | 1            | 0 | 0 | 1 |  |  |  |

| 42       |         |   |   |   |   | • |   |          |   |          | • |   |   |   |   |   | 1 | 0 | 1            | 0 | 1 | 0 |  |  |  |

| 43       |         |   |   |   |   | • |   |          |   |          |   | • |   |   |   |   | 1 | 0 | 1            | 0 | 1 | 1 |  |  |  |

| 44       |         |   |   |   |   | • |   |          |   |          |   |   | • |   |   |   | 1 | 0 | 1            | 1 | 0 | 0 |  |  |  |

| 45       |         |   |   |   |   | • |   |          |   |          |   |   |   | • |   |   | 1 | 0 | 1            | 1 | 0 | 1 |  |  |  |

| 46       |         |   |   |   |   | • |   |          |   |          |   |   |   |   | • |   | 1 | 0 | 1            | 1 | 1 | 0 |  |  |  |

| 47       |         |   |   |   |   | • |   |          |   |          |   |   |   |   |   | • | 1 | 0 | 1            | 1 | 1 | 1 |  |  |  |

| 4.0      |         |   |   |   |   |   |   |          |   |          |   |   |   |   |   |   |   |   |              |   |   |   |  |  |  |

| 48       |         |   |   |   |   |   | • |          | • |          |   |   |   |   |   |   | 1 | 1 | 0            | 0 | 0 | 0 |  |  |  |

| 49       |         |   |   |   |   |   | • |          |   | •        |   |   |   |   |   |   | 1 | 1 | 0            | 0 | 0 | 1 |  |  |  |

| 50       |         |   |   |   |   |   | • |          |   |          | • | _ |   |   |   |   | 1 | 1 | 0            | 0 | 1 | 0 |  |  |  |

| 51<br>52 |         |   |   |   |   |   | • |          |   |          |   | • | _ |   |   |   | 1 | 1 | 0            | 0 | 1 | 1 |  |  |  |

| 53       |         |   |   |   |   |   | • |          |   |          |   |   | • | _ |   |   | 1 | 1 | 0            | 1 | 0 | 0 |  |  |  |

| 54       |         |   |   |   |   |   | • |          |   |          |   |   |   | • |   |   | 1 | 1 | 0            | 1 | 0 | 1 |  |  |  |

| 55       |         |   |   |   |   |   | • |          |   |          |   |   |   |   | • |   | 1 | 1 | 0            | 1 | 1 | 0 |  |  |  |

| 55       |         |   |   |   |   |   | • | ì        |   |          |   |   |   |   |   |   | 1 | 1 | 0            | 1 | 1 | 1 |  |  |  |

| 56       |         |   |   |   |   |   |   | •        | • |          |   |   |   |   |   |   | 1 | 1 | 1            | 0 | 0 | 0 |  |  |  |

| 57       |         |   |   |   |   |   |   | •        |   | •        |   |   |   |   |   |   | 1 | 1 | 1            | 0 | 0 | 1 |  |  |  |

| 58       |         |   |   |   |   |   |   | •        |   |          | • |   |   |   |   |   | 1 | 1 | 1            | 0 | 1 | 0 |  |  |  |

| 59       |         |   |   |   |   |   |   | •        |   |          |   | • |   |   |   |   | 1 | 1 | 1            | 0 | 1 | 1 |  |  |  |

| 60       |         |   |   |   |   |   |   | •        |   |          |   |   | • |   |   |   | 1 | 1 | 1            | 1 | 0 | 0 |  |  |  |

| 61       |         |   |   |   |   |   |   | •        |   |          |   |   |   | • |   |   | 1 | 1 | 1            | 1 | 0 | 1 |  |  |  |

| 62       |         |   |   |   |   |   |   | •        |   |          |   |   |   |   | • |   | 1 | 1 | 1            | 1 | 1 | 0 |  |  |  |

| 63       |         |   |   |   |   |   |   | •        |   |          |   |   |   |   |   | • | 1 | 1 | 1            | 1 | 1 | 1 |  |  |  |

Table 2 System matrix Z-DR

| system<br>no. |   | Z-lir<br>Z | <br>ne <b>s</b><br>2 |   |       |   |   |   | lines |   |   |   | system bits<br>S |   |   |   |   |  |  |  |

|---------------|---|------------|----------------------|---|-------|---|---|---|-------|---|---|---|------------------|---|---|---|---|--|--|--|

|               | 0 | 1          | 2                    | 3 | 0     | 1 | 2 | 3 | 4     | 5 | 6 | 7 | 4                | 3 | 2 | 1 | 0 |  |  |  |

| 0             | • |            |                      |   | •     |   |   |   |       |   |   |   | 0                | 0 | 0 | 0 | 0 |  |  |  |

| 1             | • |            |                      |   |       | • |   |   |       |   |   |   | 0                | 0 | 0 | 0 | 1 |  |  |  |

| 2             | • |            |                      |   |       |   | • |   |       |   |   |   | 0                | 0 | 0 | 1 | 0 |  |  |  |

| 3             | • |            |                      |   |       |   |   | • |       |   |   |   | 0                | 0 | 0 | 1 | 1 |  |  |  |

| 4             | • |            |                      |   |       |   |   |   | •     |   |   |   | 0                | 0 | 1 | 0 | 0 |  |  |  |

| 5             | • |            |                      |   |       |   |   |   |       | • |   |   | 0                | 0 | 1 | 0 | 1 |  |  |  |

| 6             | • |            |                      |   |       |   |   |   |       |   | • |   | 0                | 0 | 1 | 1 | 0 |  |  |  |

| 7             | • |            |                      |   |       |   |   |   |       |   |   | • | 0                | 0 | 1 | 1 | 1 |  |  |  |

| 8             |   | •          |                      |   | •     |   |   |   |       |   |   |   | 0                | 1 | 0 | 0 | 0 |  |  |  |

| 9             |   | •          |                      |   |       | • |   |   |       |   |   |   | 0                | 1 | 0 | 0 | 1 |  |  |  |

| 10            |   | •          |                      |   |       |   | • |   |       |   |   |   | 0                | 1 | 0 | 1 | 0 |  |  |  |

| 11            |   | •          |                      |   |       |   |   | • |       |   |   |   | 0                | 1 | 0 | 1 | 1 |  |  |  |

| 12            |   | •          |                      |   |       |   |   |   | •     |   |   |   | 0                | 1 | 1 | 0 | 0 |  |  |  |

| 13            |   | •          |                      |   |       |   |   |   |       | • |   |   | 0                | 1 | 1 | 0 | 1 |  |  |  |

| 14            |   | •          |                      |   |       |   |   |   |       |   | • |   | 0                | 1 | 1 | 1 | 0 |  |  |  |

| 15            |   | •          |                      |   |       |   |   |   |       |   |   | • | 0                | 1 | 1 | 1 | 1 |  |  |  |

| 16            |   |            | •                    |   | è     |   |   |   |       |   |   |   | 1                | 0 | 0 | 0 | 0 |  |  |  |

| 17            |   |            | •                    |   | ļ<br> | • |   |   |       |   |   |   | 1                | 0 | 0 | 0 | 1 |  |  |  |

| 18            |   |            | •                    |   |       |   | • |   |       |   |   |   | 1                | 0 | 0 | 1 | 0 |  |  |  |

| 19            |   |            | •                    |   |       |   |   | • |       |   |   |   | 1                | 0 | 0 | 1 | 1 |  |  |  |

| 20            |   |            | •                    |   |       |   |   |   | •     |   |   |   | 1                | 0 | 1 | 0 | 0 |  |  |  |

| 21            |   |            | •                    |   |       |   |   |   |       | • |   |   | 1                | 0 | 1 | 0 | 1 |  |  |  |

| 22            |   |            | •                    |   | ĺ     |   |   |   |       |   | • |   | 1                | 0 | 1 | 1 | 0 |  |  |  |

| 23            |   |            | •                    |   |       |   |   |   |       |   |   | • | 1                | 0 | 1 | 1 | 1 |  |  |  |

| 24            |   |            |                      | • |       |   |   |   |       |   |   |   | 1                | 1 | 0 | 0 | 0 |  |  |  |

| 25            |   |            |                      | • |       | • |   |   |       |   |   |   | 1                | 1 | 0 | 0 | 1 |  |  |  |

| 26            |   |            |                      | • |       |   | • |   |       |   |   |   | 1                | 1 | 0 | 1 | 0 |  |  |  |

| 27            |   |            |                      | • |       |   |   | • |       |   |   |   | 1                | 1 | 0 | 1 | 1 |  |  |  |

| 28            |   |            |                      | • |       |   |   |   | •     |   |   |   | 1                | 1 | 1 | 0 | 0 |  |  |  |

| 29            |   |            |                      | • |       |   |   |   |       | • |   |   | 1                | 1 | 1 | 0 | 1 |  |  |  |

| 30            |   |            |                      | • |       |   |   |   |       |   | • |   | 1                | 1 | 1 | 1 | 0 |  |  |  |

| 31            |   |            |                      | • |       |   |   |   |       |   |   | • | 1                | 1 | 1 | 1 | 1 |  |  |  |

| 0.            |   |            |                      |   |       |   |   |   |       |   |   |   |                  |   | • |   | • |  |  |  |

## **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage range with respect to VSS         | $v_{DD}$  | -0,5 to +15                       | V    |  |  |  |

|--------------------------------------------------|-----------|-----------------------------------|------|--|--|--|

| Input voltage range                              | VI        | -0,5 to (V <sub>DD</sub> +0,5) V* |      |  |  |  |

| Input current                                    | ± IĮ      | max. 10                           | mΑ   |  |  |  |

| Output voltage range                             | $v_0$     | $-0.5$ to $(V_{DD} + 0.5)$        | ) V* |  |  |  |

| Output current                                   | ± IO      | max. 10                           | mΑ   |  |  |  |

| Power dissipation output OSCO                    | PO        | max. 50                           | mW   |  |  |  |

| Power dissipation per output (all other outputs) | PO        | max. 100                          | mW   |  |  |  |

| Total power dissipation per package              | $P_{tot}$ | max. 200                          | mW   |  |  |  |

| Operating ambient temperature range              | $T_{amb}$ | -25 to +85                        | oC   |  |  |  |

| Storage temperature range                        | $T_{stg}$ | -55 to +150                       | оС   |  |  |  |

## **HANDLING**

Inputs and outputs are protected against electrostatic charge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see "Handling MOS Devices").

<sup>\*</sup>  $V_{DD}$  + 0,5 V not to exceed 15 V.

## **CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = -25 to 85 °C unless otherwise specified

| parameter                                                                                                                                                                                                                                    | V <sub>DD</sub> (V) | symbol           | min.                  | typ. | max.                  | unit    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|-----------------------|------|-----------------------|---------|

| Supply voltage                                                                                                                                                                                                                               |                     | V <sub>DD</sub>  | 4,75                  | _    | 12,6                  | v       |

| Supply current at I <sub>O</sub> = 0 mA for all outputs; X0 to X7 and Z3 at V <sub>DD</sub> ; all other inputs at V <sub>DD</sub> or V <sub>SS</sub> ; excluding leakage current from open drain N-channel outputs; T <sub>amb</sub> = 25 °C | 12,6                | I <sub>DD</sub>  | _                     | _    | 10                    | μА      |

| Inputs                                                                                                                                                                                                                                       |                     |                  |                       |      |                       |         |

| Keyboard inputs X and Z with<br>P-channel pull-up transistors                                                                                                                                                                                |                     |                  | :                     |      |                       |         |

| Input current (each input) at $V_1 = 0 V$ ;<br>TP = SSM = LOW                                                                                                                                                                                | 4,75 to 12,6        | I <sub>I</sub>   | 10                    | -    | 300                   | μΑ      |

| Input voltage HIGH                                                                                                                                                                                                                           | 4,75 to 12,6        | VIH              | 0,7 x V <sub>DD</sub> | _    | V <sub>DD</sub>       | V       |

| Input voltage LOW                                                                                                                                                                                                                            | 4,75 to 12,6        | VIL              | 0                     | _    | 0,3 x V <sub>DD</sub> | V       |

| Input leakage current at T <sub>amb</sub> = 25 °C;<br>TP = HIGH;                                                                                                                                                                             | 10.0                |                  |                       |      |                       | _       |

| V <sub>I</sub> = 12,6 V                                                                                                                                                                                                                      | 12,6                | <sup>I</sup> IR  | _                     | _    | 1                     | μΑ      |

| $V_{\parallel} = 0 V$                                                                                                                                                                                                                        | 12,6                | −¹IR             | _                     | _    | 1                     | μΑ      |

| SSM, TP and OSCI inputs                                                                                                                                                                                                                      | 4.75 40.0           |                  | 07 1/                 |      |                       |         |

| Input voltage HIGH                                                                                                                                                                                                                           | 4,75 to 12,6        |                  | 0,7 × V <sub>DD</sub> |      | V <sub>DD</sub>       | V       |

| Input lookers surrent at T                                                                                                                                                                                                                   | 4,75 to 12,6        | VIL              | 0                     | _    | 0,3 × V <sub>DD</sub> | V       |

| Input leakage current at $T_{amb} = 25  ^{\circ}\text{C}$ ; $V_1 = 12,6  \text{V}$                                                                                                                                                           | 12,6                | IR               | _                     | _    | 1                     | μΑ      |

| V <sub>1</sub> = 0 V                                                                                                                                                                                                                         | 12,6                | -l <sub>IR</sub> | -                     | _    | 1                     | μΑ      |

| Outputs                                                                                                                                                                                                                                      |                     |                  |                       |      |                       |         |

| DATA, MDATA outputs                                                                                                                                                                                                                          |                     |                  |                       |      |                       |         |

| Output voltage HIGH at $-I_{OH}$ = 0,8 mA                                                                                                                                                                                                    | 4,75 to 12,6        | Vон              | V <sub>DD</sub> – 0,6 | _    | _                     | V       |

| Output voltage LOW at IOL = 0,8 mA                                                                                                                                                                                                           | 4,75 to 12,6        | ĺ                | _                     | _    | 0,4                   | V       |

| Output leakage current at:                                                                                                                                                                                                                   |                     |                  |                       |      |                       |         |

| V <sub>O</sub> = 12,6 V                                                                                                                                                                                                                      | 12,6                | IOR              | -                     | -    | 10                    | $\mu$ A |

| V <sub>O</sub> = 0 V                                                                                                                                                                                                                         | 12,6                | -IOR             | -                     | -    | 20                    | μΑ      |

| T <sub>amb</sub> = 25 <sup>o</sup> C;<br>V <sub>O</sub> = 12,6 V                                                                                                                                                                             | 12.6                | 1                |                       |      |                       |         |

| V <sub>O</sub> = 12,6 V<br>V <sub>O</sub> = 0 V                                                                                                                                                                                              | 12,6                | OR               | -                     | _    | 1                     | μΑ      |

| ν O - 0 ν                                                                                                                                                                                                                                    | 12,6                | <sup>−l</sup> OR | -                     | -    | 2                     | μΑ      |

| parameter                                                                      | V <sub>DD</sub> (V) | symbol          | min.                 | typ. | max. | unit |

|--------------------------------------------------------------------------------|---------------------|-----------------|----------------------|------|------|------|

| DR0 to DR7 outputs                                                             |                     |                 |                      |      |      |      |

| Output voltage LOW;<br>at IOL = 0,35 mA                                        | 4,75 to 12,6        | VOL             | _                    |      | 0,4  | V    |

| Output leakage current at V <sub>O</sub> = 12,6 V                              | 12,6                | IOR             | -                    |      | 10   | μΑ   |

| at $V_O = 12,6 V$ ;<br>$T_{amb} = 25  {}^{o}C$<br>OSCO output                  | 12,6                | IOR             |                      |      | 1    | μΑ   |

| Output voltage HIGH<br>at -I <sub>OH</sub> = 0,2 mA;<br>OSCI = V <sub>SS</sub> | 4,75 to 12,6        | V <sub>OH</sub> | V <sub>DD</sub> -0,6 |      |      | ٧    |

| Output voltage LOW at $-I_{OL} = 0.45 \text{ mA}$ ; OSCI = $V_{DO}$            | 4,75 to 12,6        | V <sub>OL</sub> | _                    |      | 0,5  | ٧    |

| Oscillator                                                                     |                     |                 |                      |      |      |      |

| Maximum oscillator frequency                                                   |                     |                 |                      |      |      |      |

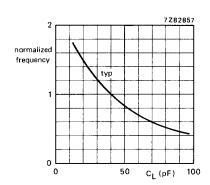

| at $C_L = 40 pF$ (Figs 6 and 7)                                                | 4,75                | fosci           | 75                   | 72   |      | kHz  |

|                                                                                | 6                   | fosci           | 120                  | 72   | -    | kHz  |

|                                                                                | 12,6                | fosci           | 300                  | 72   | _    | kHz  |

Fig. 6 Typical normalized input frequency as a function of the load (keyboard) capacitance.

Fig. 7 Test circuit for measurement of maximum oscillator frequency.